소개

- CPU 성능 요인

- 명령어 수(Instruction count) : ISA, 컴파일러에 의해 결정

- CPI와 사이클시간(Cycle time) : CPU 하드웨어에 따라 결정

- 두 가지 MIPS 구현을 검토할 것이다.

- 1. 단순화된 버전

- 2. 현실적인 파이프라인 버전

- 단순 하위 집합으로 대부분의 측면을 보여줌

- 메모리 참조 : lw, sw

- 산술/논리 : add, sub, and, or, slt

- 제어 전달 : beq, j

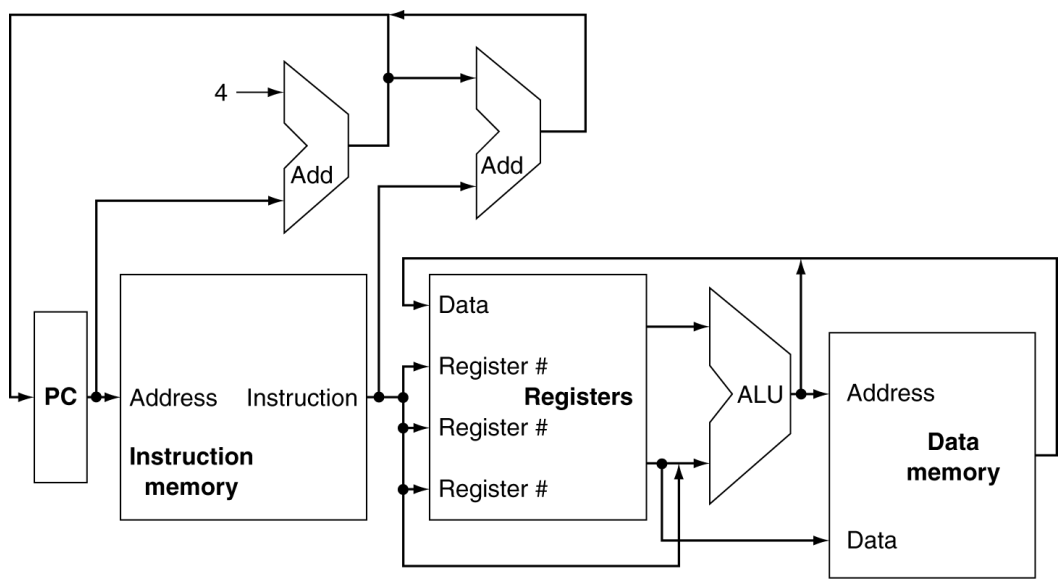

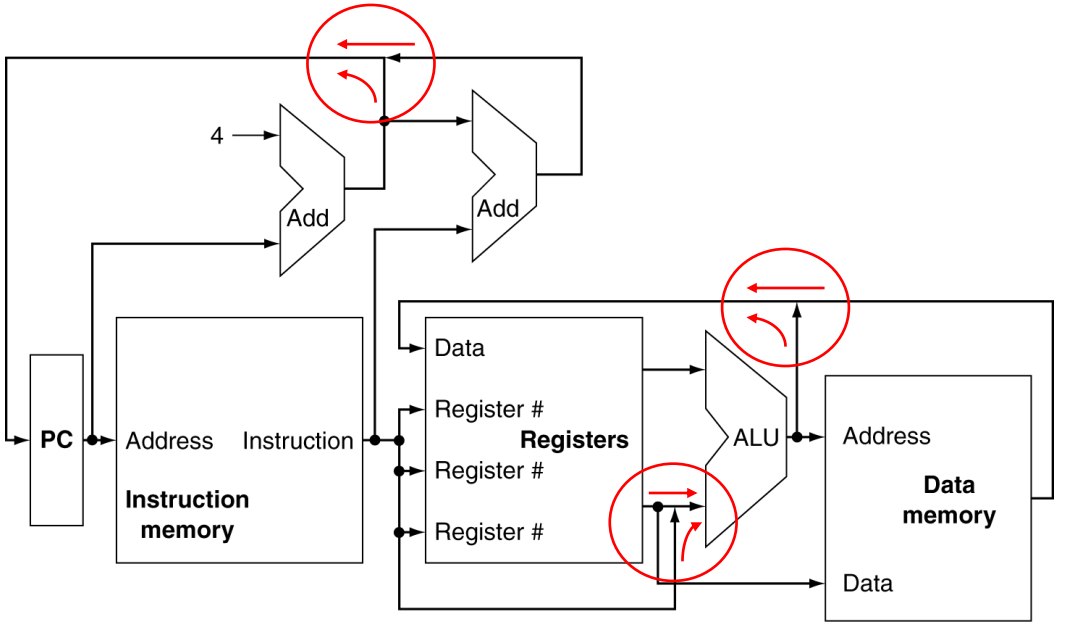

명령어 실행

- PC → 명령어 메모리, 명령어 가져오기

- 레지스터 번호 → 파일 등록, 레지스터 읽기

- 명령어 class에 따라 다르다.

- ALU를 사용하여 계산

- 산술 결과

- 로드/저장을 위한 메모리 주소

- 지점 대상 주소

- 로드/저장을 위해 데이터 메모리에 액세스

- PC : 대상 주소 or PC + 4(명령어 크기가 4이기 때문)

- ALU를 사용하여 계산

- PC(프로그램카운터) : 32bit 레지스터, 명령어 인코딩의 주소가 저장되어 있다.

- 명령어를 디코딩한 후 해당 레지스터에 접근하고, 레지스터에 있는 값을 가지고 연산한다.

CPU 개요

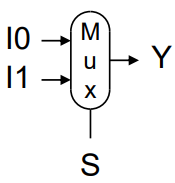

- 멀티플랙서(Multiplexer) : 와이어를 그냥 연결할 수는 없기때문에 멀티플렉서 사용

논리 설계

- 이진수로 인코딩된 정보

- 저전압 = 0, 고전압 = 1

- 비트당 와이어 1개

- 다중 와이어 버스에 인코딩된 다중 비트 데이터

- 조합 요소(Combinational Elements)

- 데이터 작업

- 출력은 입력의 함수

- 순차 요소(Sequential elements)

- 저장 정보

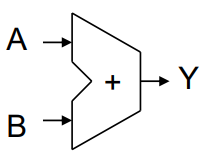

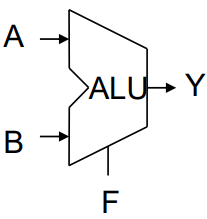

조합 요소(Combinational Elements)

| AND-gate | Y = A & B |  |

| Adder | Y = A + B |  |

| Multiplexer | Y = S ? I1 : I0 |  |

| Arithmetic/Logic Unit | Y = F(A, B) |  |

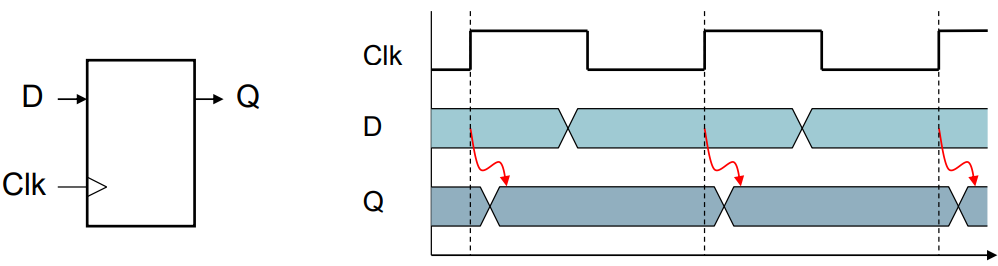

순차 요소(Sequential elements)

- 레지스터 : 회로에 데이터를 저장

- 클록 신호를 사용하여 저장된 값을 업데이트할 시기를 결정한다.

- Edge-triggered : Clk가 0 → 1로 변경될 때 업데이트된다.

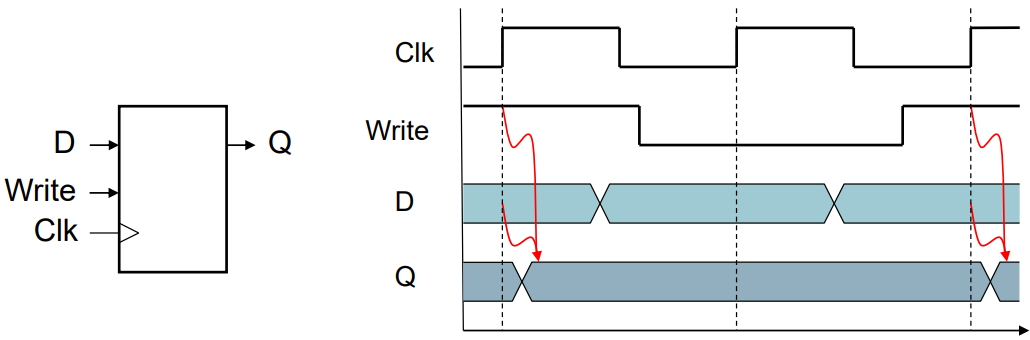

- Write 제어 레지스터

- Write 제어 입력이 1인 경우만 클럭 에지 업데이트된다.

- 나중에 저장된 값이 필요할 때 사용한다.

- 클럭 시그널이 0 → 1로 바뀌며 동시에 write 시그널이 1일때만 업데이트된다.

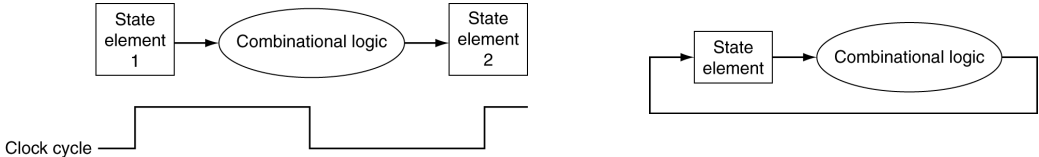

Clocking 방법론

- 조합 논리는 클록 주기 동안 데이터를 변환한다.

- 클록 에지 사이

- 상태 요소(state elements)에서 입력, 상태 요소(state elements)로 출력

- 가장 긴 지연이 클록 주기를 결정

- 여러 연산 수행이 있을때 결국 가장 연산이 느린 것으로 맞춰짐

'컴퓨터시스템구조' 카테고리의 다른 글

| [컴퓨터시스템구조] 18. MIPS 부동 소수점 연산자 (1) | 2023.10.19 |

|---|---|

| [컴퓨터시스템구조] 17. 부동 소수점 (1) | 2023.10.15 |

| [컴퓨터시스템구조] 16. 컴퓨터 산술(mult, mfhi, mflo, mul, div) (0) | 2023.10.15 |

| [컴퓨터시스템구조] 15. MIPS 배열 vs. 포인터 (0) | 2023.10.15 |

| [컴퓨터시스템구조] 14. MIPS Sort (1) | 2023.10.15 |

댓글