데이터패스(Datapath) 구축

- 데이터패스

- CPU에서 데이터와 주소를 처리하는 요소

- 레지스터, ALU, 멀티플렉서, 메모리, …

- MIPS 데이터패스를 점진적으로 구축

- 점점 개요 디자인 개선

- CPU 안에 어떻게 연결(위치) 시킬 것인가

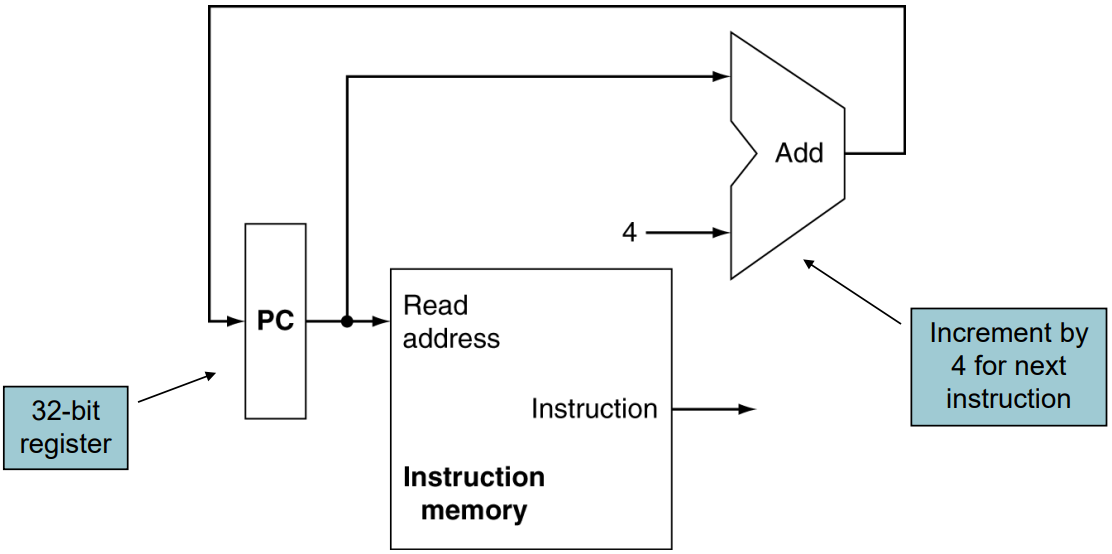

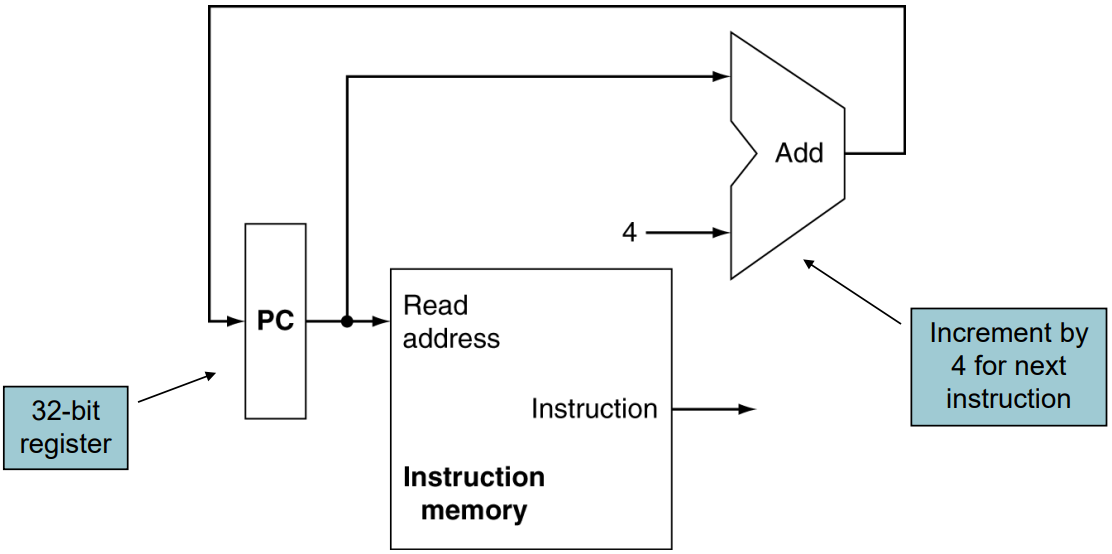

명령어 가져오기(Fetch)

- 어떠어떠한 하드웨어가 필요한가

- 일단 32비트 레지스터 PC 필요 : 주소값 저장 용도

- 다음 명령을 위해 4씩 증가

- 일단 32비트 레지스터 PC 필요 : 주소값 저장 용도

R-포맷 명령어

| op | rs | rt | rd | shamt | funct |

- 두 개의 레지스터 피연산자 읽기

- 산술/논리 연산 수행

- 레지스터 결과 쓰기

| 예) add $s0, $s1, $s2 | |

| Read register 1 | $s1 |

| Read register 2 | $s2 |

| Write register | $s0 |

| Write Data | Read data 1, 2를 통해 $s1, $s2를 ALU로 옮기고 ALU 결과를 Write Data 레지스터에 저장 |

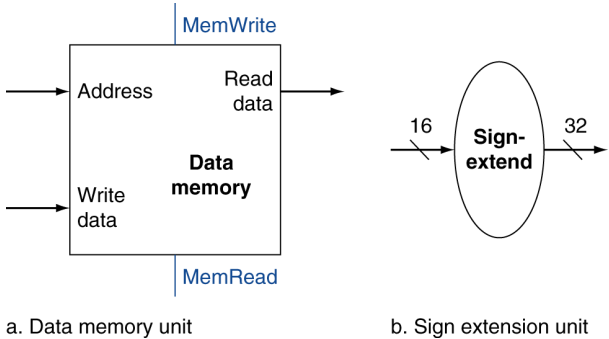

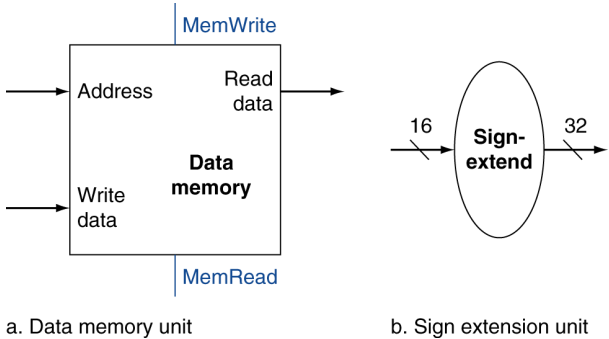

Load/Store 명령어

| op | rs | rt | offset |

- 레지스터 피연산자 읽기

- 16비트 오프셋을 사용하여 주소 계산

- ALU를 사용하지만 부호 확장 오프셋

- 로드(Load) : 메모리 읽기 및 레지스터 업데이트

- 저장(Store) : 레지스터 값을 메모리에 쓰기

- 레지스터를 두개 읽음

| 예) sw $t0, 4($s1) $s1의 베이스주소를 통해 값을 읽어오고 $t0에 저장 |

|

| Read register 1 | $s1의 베이스주소 |

| Read register 2 | 오프셋 |

| 예) lw $t0, 4($s1) $s1의 베이스주소에 $t0 값을 저장 |

|

| Read register 1 | $s1의 베이스주소 |

| Write register | 오프셋 |

- Write 시그널이 1일 때 MemWrite가 1

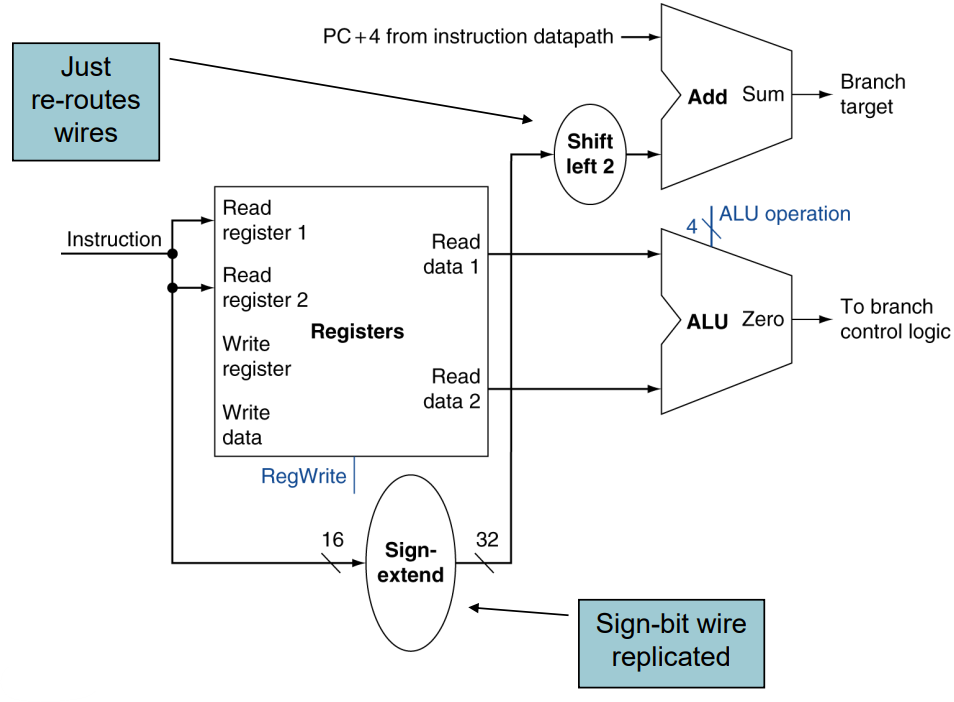

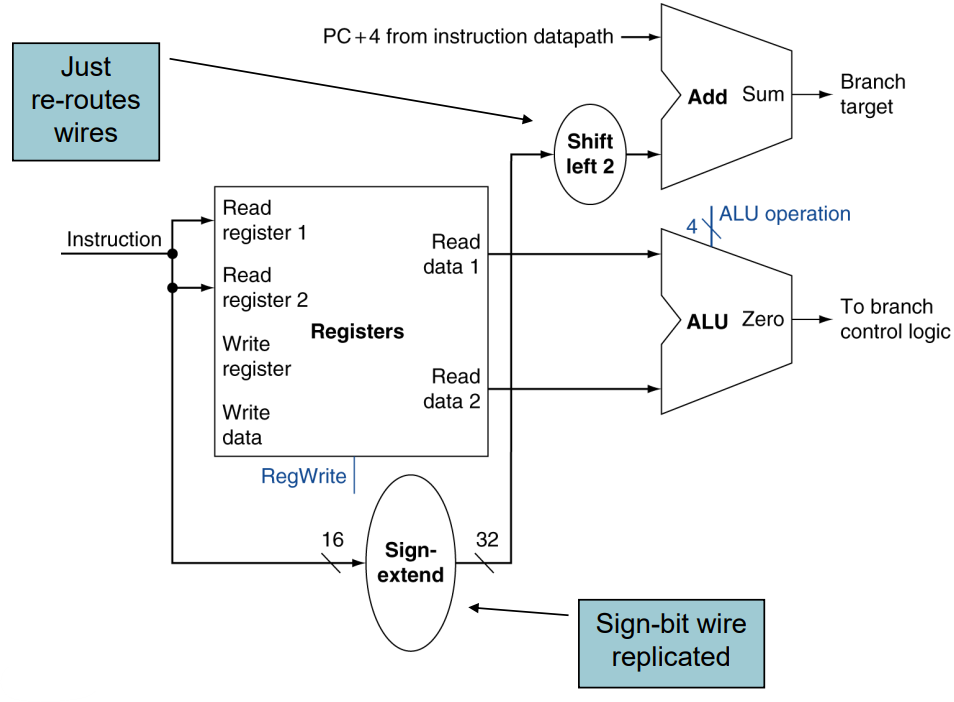

Branch 명령어

- 레지스터 피연산자 읽기

- 피연산자 비교

- ALU를 사용, 두 레지스터를 빼서 Zero 출력인지 확인

- 대상 주소 계산

- 부호 확장 변위

- 왼쪽으로 2자리 이동(워드 치환)

- PC + 4에 추가

- 명령어 패치로 이미 계산됨

- 대상 주소 = PC(프로그램카운터) + 오프셋 × 4

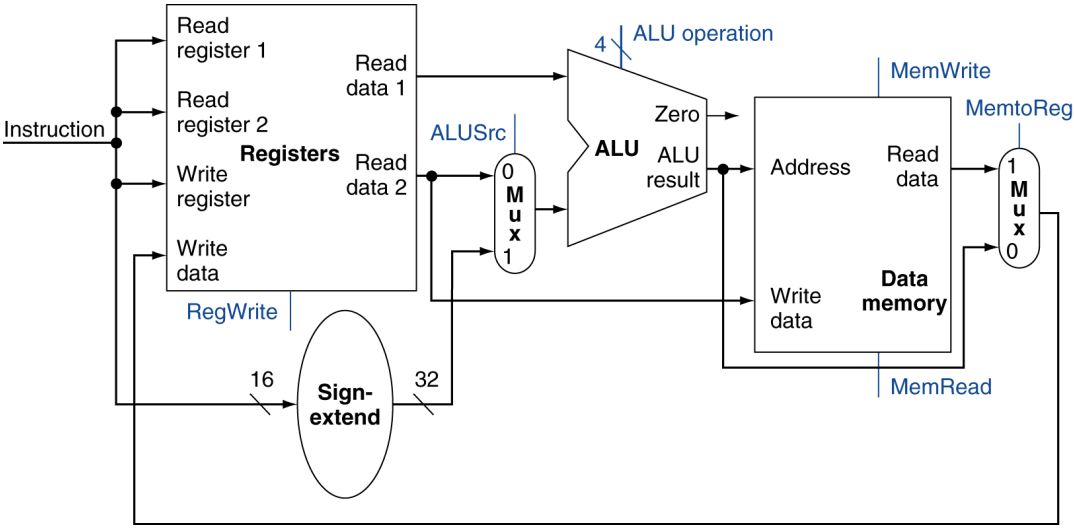

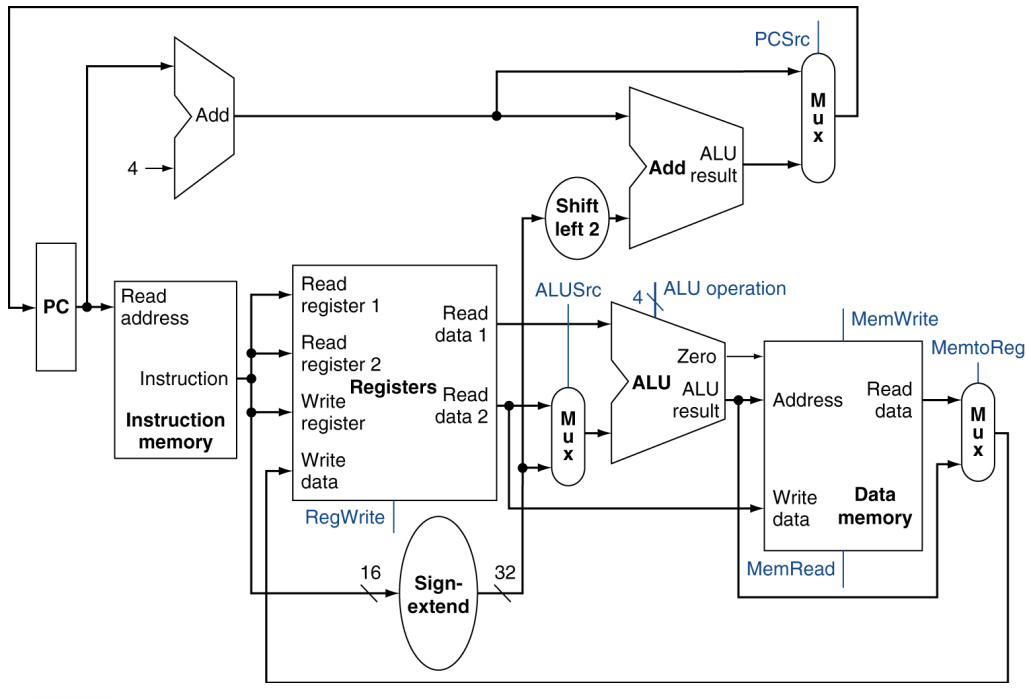

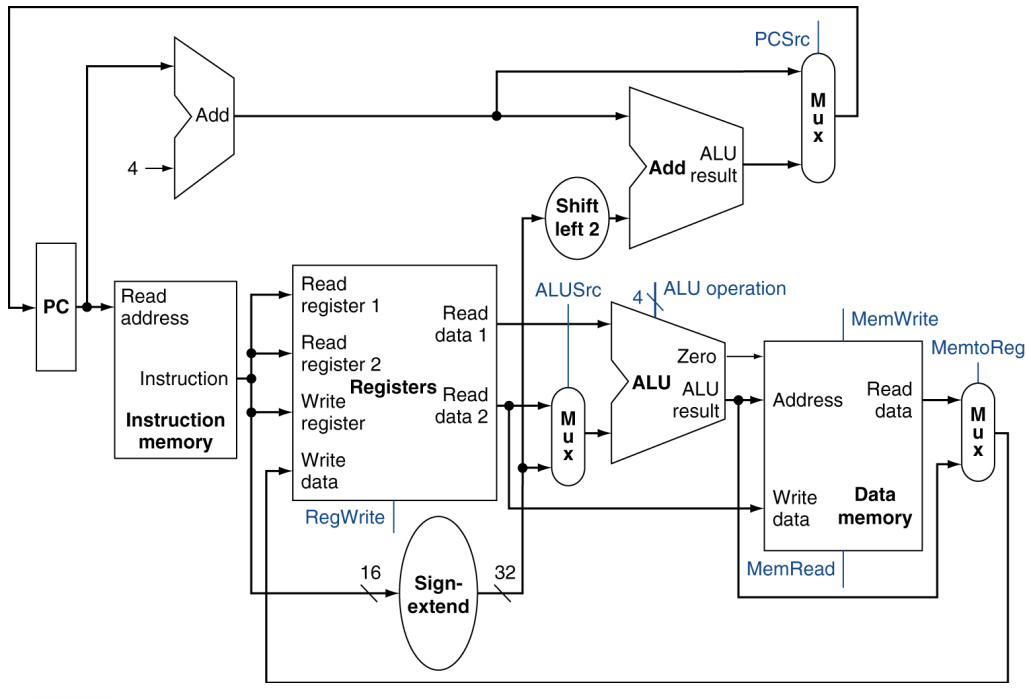

요소 구성

- First-cut 데이터패스 : 한 클록 주기에 명령을 수행한다.

- 각 데이터패스 요소는 한 번에 하나의 기능만 수행 가능

- 따라서 별도의 명령어와 데이터 메모리가 필요

- 다른 명령에 대체 데이터 소스가 사용되는 경우 멀티플렉서를 사용

- 명령어 메모리와 데이터 메모리를 구분해서 생각

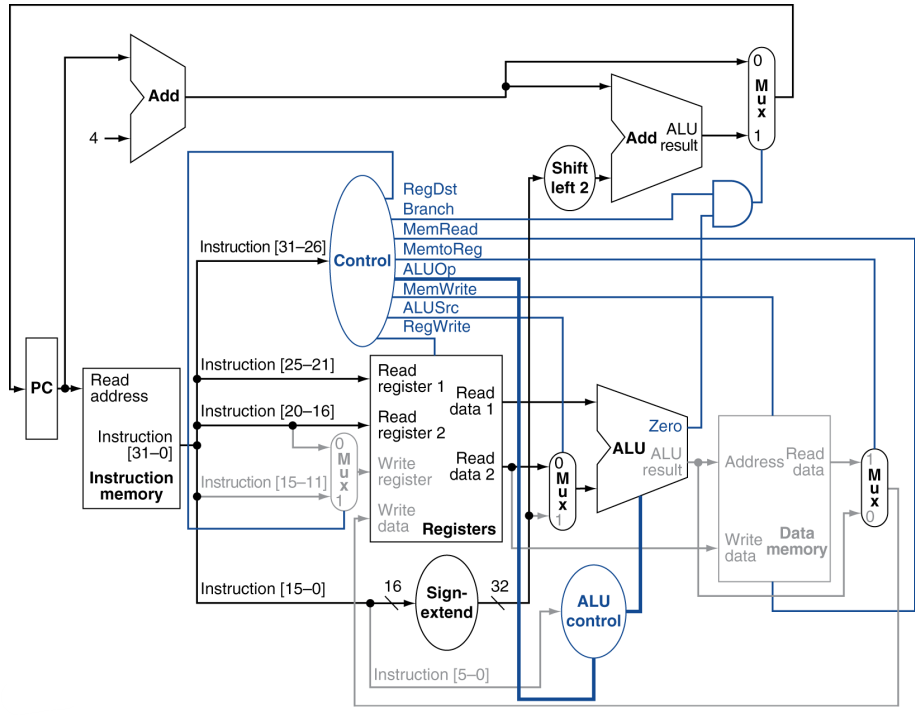

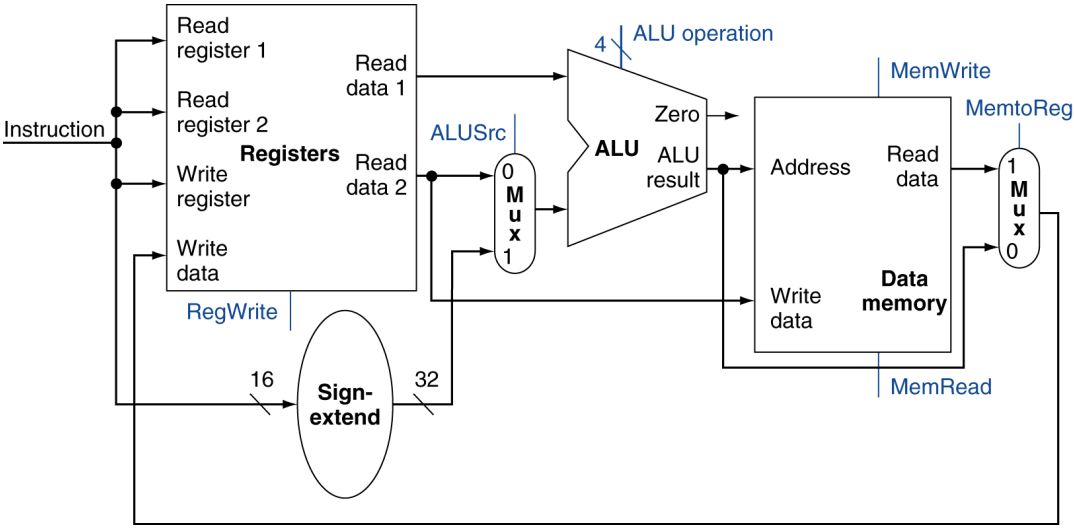

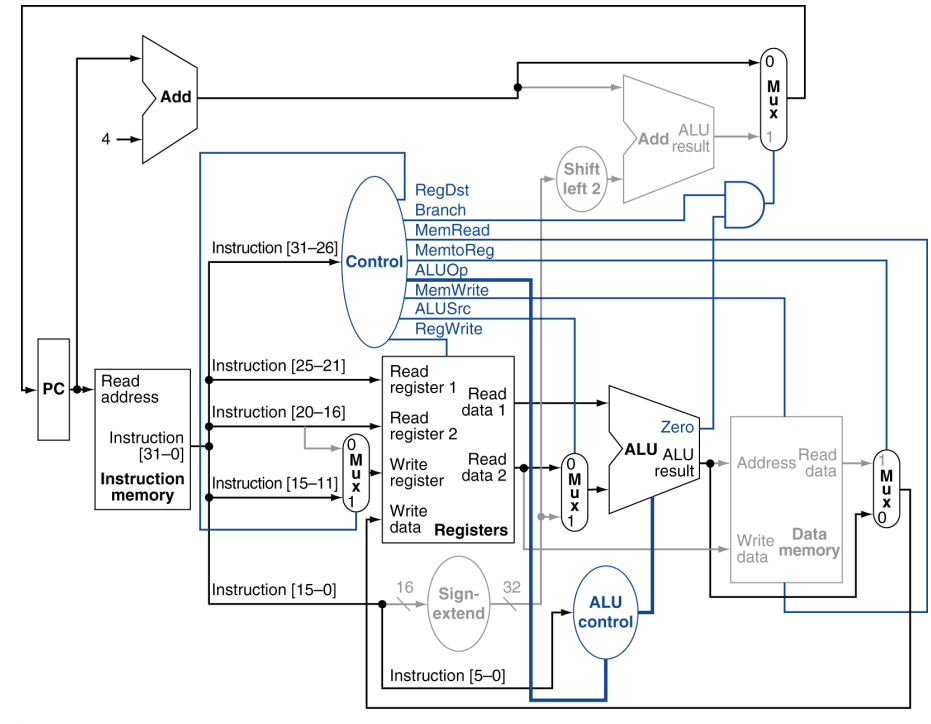

R-포맷/Load/Store 데이터패스

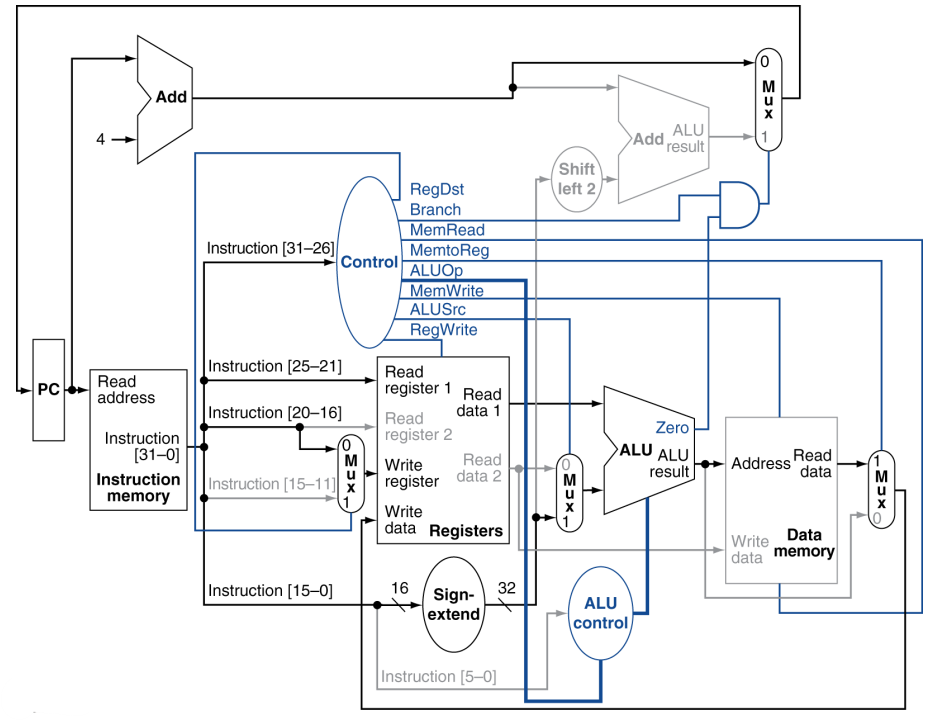

R-포맷/Load/Store/Branch 데이터패스

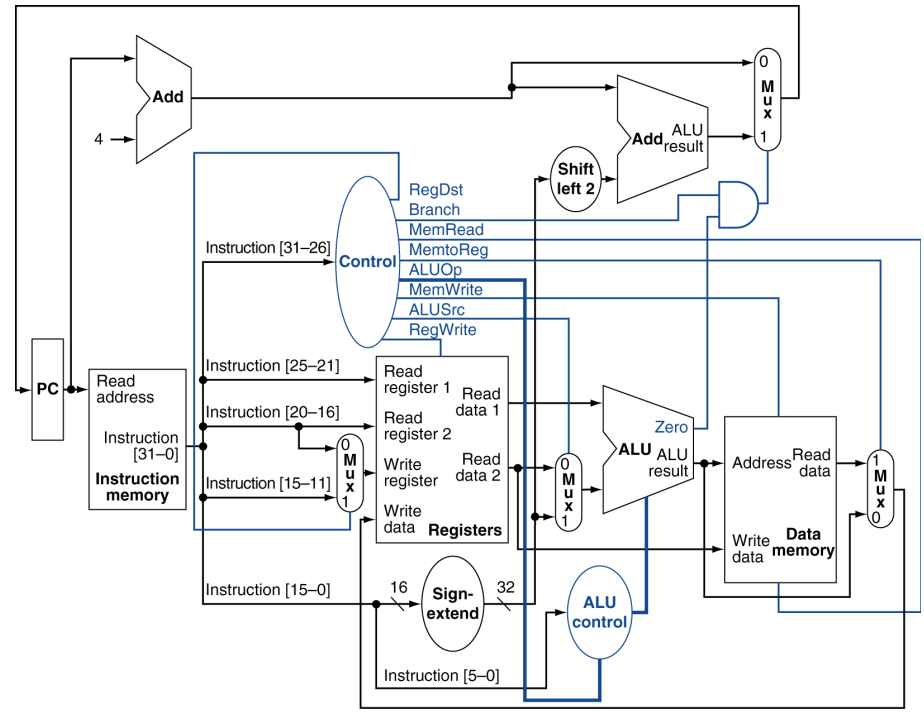

ALU 컨트롤

- Load/Store : F = add

- Branch : F = subtract

- R-type : F는 함수 필드에 따라 달라짐

| ALU 컨트롤 | 기능 |

| 0000 | AND |

| 0001 | OR |

| 0010 | add |

| 0110 | subtract |

| 0111 | set-on-less-than |

| 1100 | NOR |

- 미리 ALU를 정해두었다.

- opcode에서 파생된 2비트 ALUOp를 가정한다.

- 조합 논리로 ALU 컨트롤 유도

| opcode | ALUOp | Operation | funct | ALU function | ALU control |

| lw | 00 | load word | XXXXXX | add | 0010 |

| sw | 00 | store word | XXXXXX | add | 0010 |

| beq | 01 | branch equal | XXXXXX | subtract | 0110 |

| R-type | 10 | add | 100000 | add | 0010 |

| subtract | 100010 | subtract | 0110 | ||

| AND | 100100 | AND | 0000 | ||

| OR | 100101 | OR | 0001 | ||

| set-on-less-than | 101010 | set-on-less-than | 0111 |

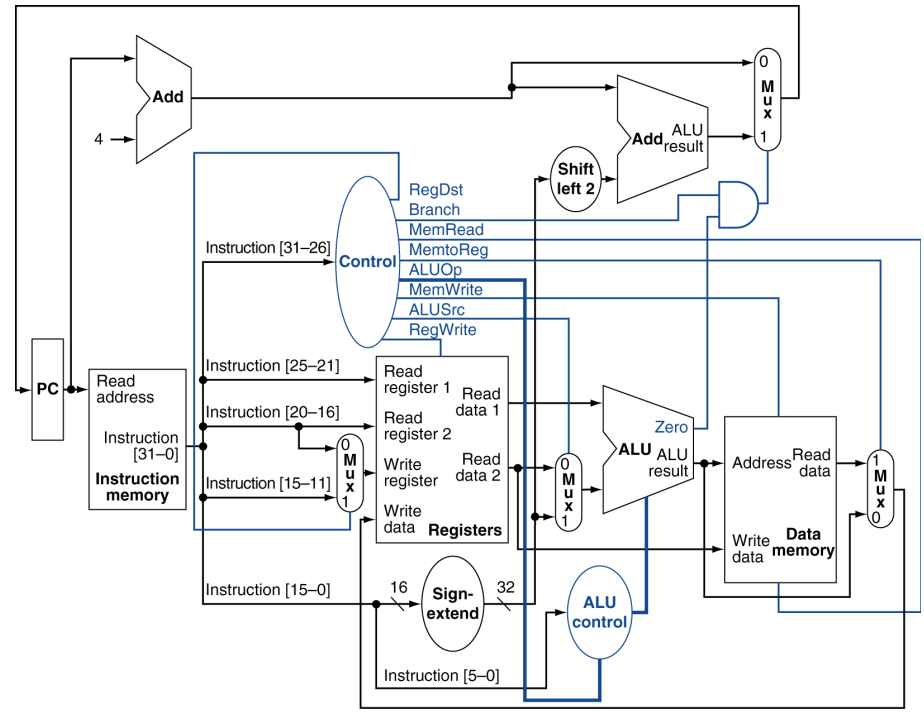

주 컨트롤 유닛

- 명령에서 파생된 제어 신호

| opcode | 항상 read | load 제외 read | R-포맷과 load 위한 write | sign-extend과 add | |||

| R-포맷 | 0 | rs | rt | rd | shamt | funct | |

| 31:26 | 25:21 | 20:16 | 15:11 | 10:6 | 5:0 | ||

| Load/Store | 35 or 43 | rs | rt | address | |||

| 31:26 | 25:21 | 20:16 | 15:0 | ||||

| Branch | 4 | rs | rt | address | |||

| 31:26 | 25:21 | 20:16 | 15:0 | ||||

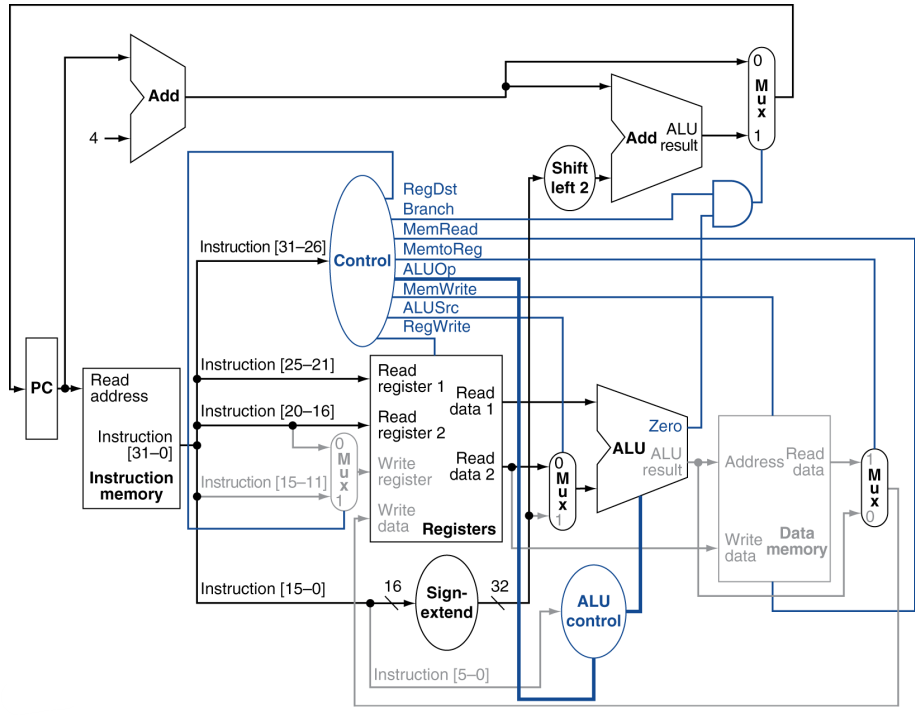

컨트롤 데이터패스

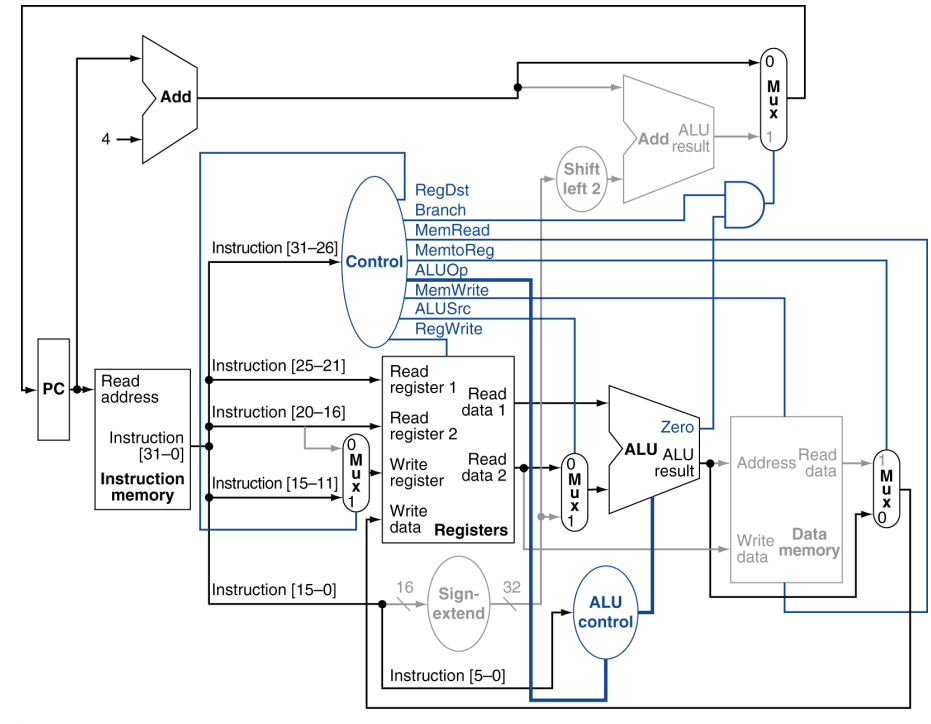

R-포맷 데이터패스

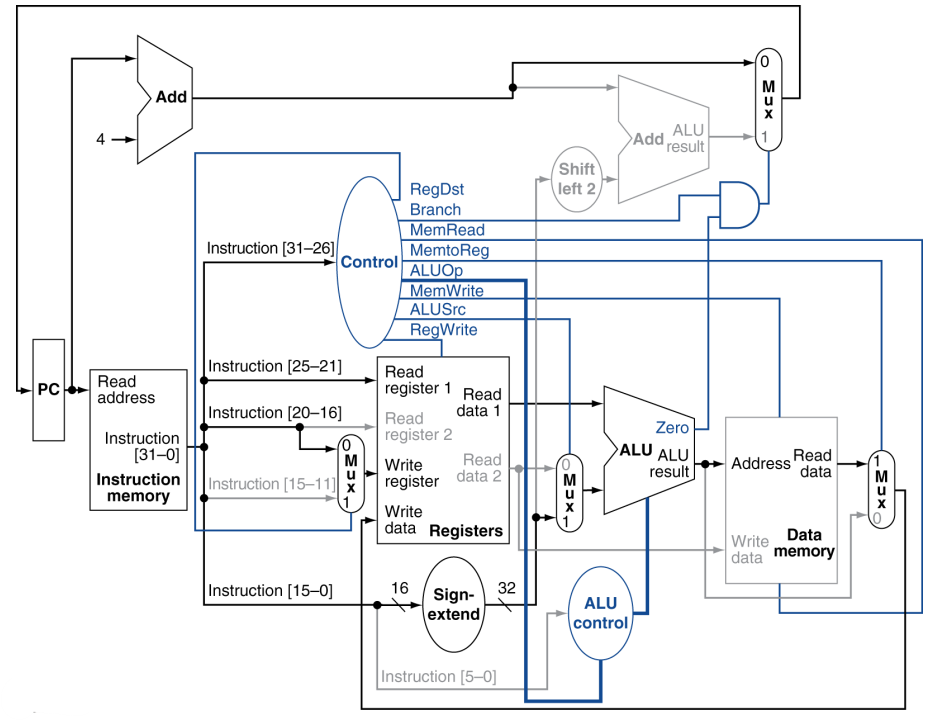

Load 데이터패스

Branch-on-Equal 데이터패스

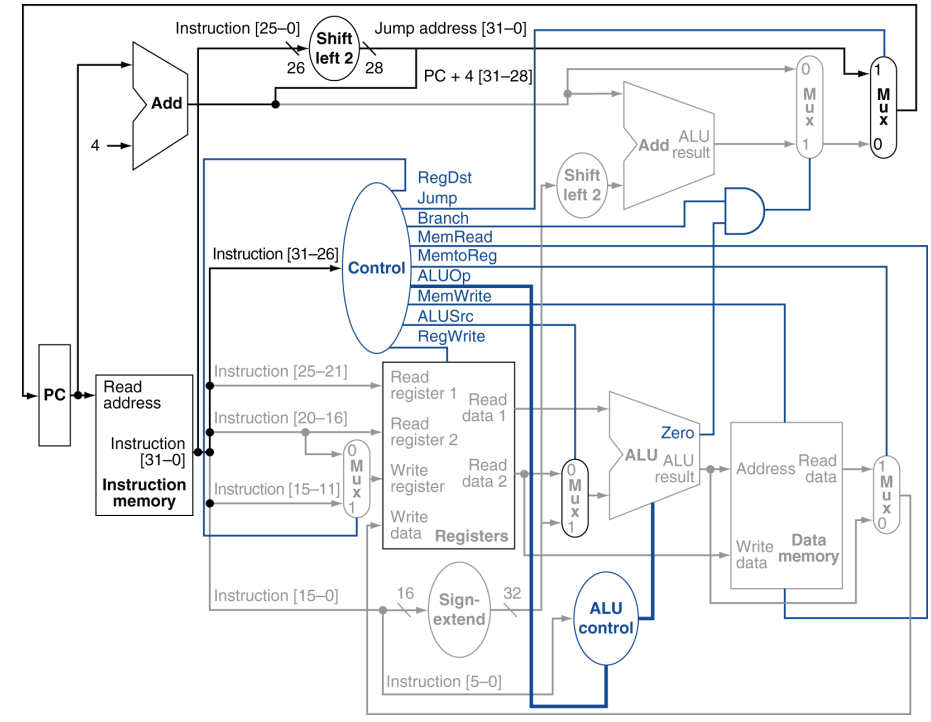

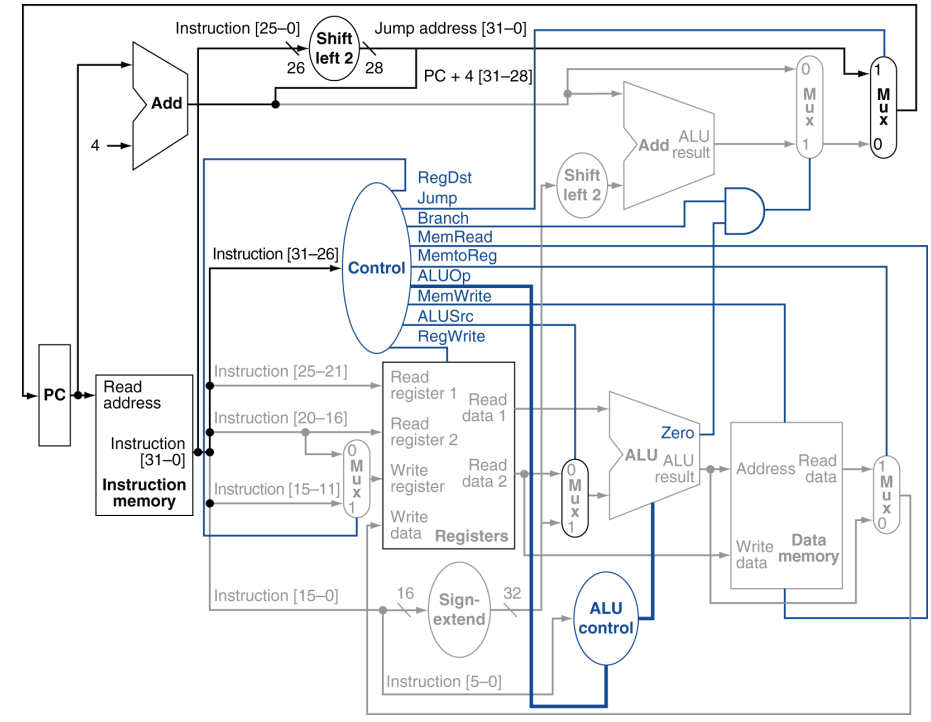

Jump 구현

| 2 | address |

| 31:26 | 25:0 |

- Jump는 워드 주소를 사용

- PC 업데이트

- 이전 PC의 상위 4비트

- 26비트 점프 주소

- 00

- 현재 PC의 상위 4비트를 붙이고, 하위 28비트는 J 포맷 안에 있는 26비트 주소 + 00 2비트

- Opcode에서 디코딩된 추가 제어 신호가 필요하다.

- 26비트를 가지고 34비트 주소를 만들어야함

Jump 데이터패스

성능 문제

- 가장 긴 지연이 클록 주기를 결정

- 가장 오래걸리는 패스 : 로드 명령

- 명령어 메모리 → 레지스터 파일 → ALU → 데이터 메모리 → 레지스터 파일

- 다른 명령어에 따라 기간을 변경할 수 없음

- 설계원칙 위반

- 일반적인 경우를 빠르게 만들기

- 파이프라이닝을 통해 성능을 향상

데이터패스(Datapath) 구축

- 데이터패스

- CPU에서 데이터와 주소를 처리하는 요소

- 레지스터, ALU, 멀티플렉서, 메모리, …

- MIPS 데이터패스를 점진적으로 구축

- 점점 개요 디자인 개선

- CPU 안에 어떻게 연결(위치) 시킬 것인가

명령어 가져오기(Fetch)

- 어떠어떠한 하드웨어가 필요한가

- 일단 32비트 레지스터 PC 필요 : 주소값 저장 용도

- 다음 명령을 위해 4씩 증가

- 일단 32비트 레지스터 PC 필요 : 주소값 저장 용도

R-포맷 명령어

| op | rs | rt | rd | shamt | funct |

- 두 개의 레지스터 피연산자 읽기

- 산술/논리 연산 수행

- 레지스터 결과 쓰기

| 예) add $s0, $s1, $s2 | |

| Read register 1 | $s1 |

| Read register 2 | $s2 |

| Write register | $s0 |

| Write Data | Read data 1, 2를 통해 $s1, $s2를 ALU로 옮기고 ALU 결과를 Write Data 레지스터에 저장 |

Load/Store 명령어

| op | rs | rt | offset |

- 레지스터 피연산자 읽기

- 16비트 오프셋을 사용하여 주소 계산

- ALU를 사용하지만 부호 확장 오프셋

- 로드(Load) : 메모리 읽기 및 레지스터 업데이트

- 저장(Store) : 레지스터 값을 메모리에 쓰기

- 레지스터를 두개 읽음

| 예) sw $t0, 4($s1) $s1의 베이스주소를 통해 값을 읽어오고 $t0에 저장 |

|

| Read register 1 | $s1의 베이스주소 |

| Read register 2 | 오프셋 |

| 예) lw $t0, 4($s1) $s1의 베이스주소에 $t0 값을 저장 |

|

| Read register 1 | $s1의 베이스주소 |

| Write register | 오프셋 |

- Write 시그널이 1일 때 MemWrite가 1

Branch 명령어

- 레지스터 피연산자 읽기

- 피연산자 비교

- ALU를 사용, 두 레지스터를 빼서 Zero 출력인지 확인

- 대상 주소 계산

- 부호 확장 변위

- 왼쪽으로 2자리 이동(워드 치환)

- PC + 4에 추가

- 명령어 패치로 이미 계산됨

- 대상 주소 = PC(프로그램카운터) + 오프셋 × 4

요소 구성

- First-cut 데이터패스 : 한 클록 주기에 명령을 수행한다.

- 각 데이터패스 요소는 한 번에 하나의 기능만 수행 가능

- 따라서 별도의 명령어와 데이터 메모리가 필요

- 다른 명령에 대체 데이터 소스가 사용되는 경우 멀티플렉서를 사용

- 명령어 메모리와 데이터 메모리를 구분해서 생각

R-포맷/Load/Store 데이터패스

R-포맷/Load/Store/Branch 데이터패스

ALU 컨트롤

- Load/Store : F = add

- Branch : F = subtract

- R-type : F는 함수 필드에 따라 달라짐

| ALU 컨트롤 | 기능 |

| 0000 | AND |

| 0001 | OR |

| 0010 | add |

| 0110 | subtract |

| 0111 | set-on-less-than |

| 1100 | NOR |

- 미리 ALU를 정해두었다.

- opcode에서 파생된 2비트 ALUOp를 가정한다.

- 조합 논리로 ALU 컨트롤 유도

| opcode | ALUOp | Operation | funct | ALU function | ALU control |

| lw | 00 | load word | XXXXXX | add | 0010 |

| sw | 00 | store word | XXXXXX | add | 0010 |

| beq | 01 | branch equal | XXXXXX | subtract | 0110 |

| R-type | 10 | add | 100000 | add | 0010 |

| subtract | 100010 | subtract | 0110 | ||

| AND | 100100 | AND | 0000 | ||

| OR | 100101 | OR | 0001 | ||

| set-on-less-than | 101010 | set-on-less-than | 0111 |

주 컨트롤 유닛

- 명령에서 파생된 제어 신호

| opcode | 항상 read | load 제외 read | R-포맷과 load 위한 write | sign-extend과 add | |||

| R-포맷 | 0 | rs | rt | rd | shamt | funct | |

| 31:26 | 25:21 | 20:16 | 15:11 | 10:6 | 5:0 | ||

| Load/Store | 35 or 43 | rs | rt | address | |||

| 31:26 | 25:21 | 20:16 | 15:0 | ||||

| Branch | 4 | rs | rt | address | |||

| 31:26 | 25:21 | 20:16 | 15:0 | ||||

컨트롤 데이터패스

R-포맷 데이터패스

Load 데이터패스

Branch-on-Equal 데이터패스

Jump 구현

| 2 | address |

| 31:26 | 25:0 |

- Jump는 워드 주소를 사용

- PC 업데이트

- 이전 PC의 상위 4비트

- 26비트 점프 주소

- 00

- 현재 PC의 상위 4비트를 붙이고, 하위 28비트는 J 포맷 안에 있는 26비트 주소 + 00 2비트

- Opcode에서 디코딩된 추가 제어 신호가 필요하다.

- 26비트를 가지고 34비트 주소를 만들어야함

Jump 데이터패스

성능 문제

- 가장 긴 지연이 클록 주기를 결정

- 가장 오래걸리는 패스 : 로드 명령

- 명령어 메모리 → 레지스터 파일 → ALU → 데이터 메모리 → 레지스터 파일

- 다른 명령어에 따라 기간을 변경할 수 없음

- 설계원칙 위반

- 일반적인 경우를 빠르게 만들기

- 파이프라이닝을 통해 성능을 향상